# Advanced Design System 2002 DSP Synthesis

February 2002

#### Notice

The information contained in this document is subject to change without notice.

Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Warranty

A copy of the specific warranty terms that apply to this software product is available upon request from your Agilent Technologies representative.

#### **Restricted Rights Legend**

Use, duplication or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DoD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies.

Agilent Technologies 395 Page Mill Road Palo Alto, CA 94304 U.S.A.

Copyright © 2002, Agilent Technologies. All Rights Reserved.

# Contents

| 1 | DSP | Synthesis | Overview |

|---|-----|-----------|----------|

|---|-----|-----------|----------|

| Launching DSP Synthesis     | 1-2 |

|-----------------------------|-----|

| Creating a New Project      | 1-3 |

| Opening an Existing Project |     |

| Importing a File            |     |

| Opening a File              |     |

| Saving a File               |     |

| Copying a File              |     |

| Closing a File              |     |

| Using Command Lines         |     |

#### 2 Behavioral Synthesis Overview

| Optimization Overview               | 2-4  |

|-------------------------------------|------|

| Using DSP Synthesis                 | 2-5  |

| Using the Synthesis Wizard          | 2-6  |

| Defining the Design Specifications  | 2-7  |

| Design Modes                        | 2-7  |

| Timing Parameters                   | 2-10 |

| Design Styles                       | 2-15 |

| Clock Periods                       | 2-16 |

| Partitioning                        | 2-19 |

| Selecting a Library                 | 2-22 |

| Mapping Libraries                   | 2-22 |

| Mapping Components                  | 2-27 |

| Estimating Resources                | 2-28 |

| Fine Estimating Resources           | 2-30 |

| Sharable and Non-Sharable Resources | 2-31 |

| Synthesizing Designs                | 2-32 |

| Timing Analysis                     | 2-33 |

|                                     |      |

#### 3 Output and Display Overview

| Generating HDL Code              | 3-1 |

|----------------------------------|-----|

| Defining HDL Specifications      | 3-2 |

| Selecting HDL Options            | 3-3 |

| Preparing for Verilog Simulation | 3-4 |

| Preparing for VHDL Simulation    | 3-5 |

| Compiling Verilog                | 3-6 |

| compile_verilog                  | 3-6 |

| compile_verilog.bat              | 3-6 |

| Compiling VHDL                   | 3-7 |

|   | compile_vhdl                               | 3-7  |

|---|--------------------------------------------|------|

|   | compile_vhdl.bat                           | 3-7  |

|   | Generating RTL HDL                         | 3-8  |

|   | Printing a Specification Report            | 3-8  |

|   | Displaying a Gantt Chart                   | 3-9  |

|   | Interpreting Results                       | 3-11 |

|   | Design Abstraction                         |      |

|   | Component Parameter Extraction             | 3-11 |

|   | Component Parameter Optimization           |      |

|   | Differences in Logic Synthesis tools       |      |

|   | Performance Reporting                      |      |

|   | Area Estimation                            | 3-12 |

| 4 | Comparing Waveforms                        |      |

|   | Customizing Waveform Comparisons           | 4-1  |

|   | Specifying Input Data                      |      |

|   | Processing Input Data                      |      |

|   | Defining Comparison Regions                |      |

|   | Defining Comparison Criteria               |      |

|   | Generating Comparison Results              |      |

|   | Input AEL Functions                        | 4-7  |

|   | awc_read_generic                           | 4-7  |

|   | awc_read_example                           | 4-8  |

|   | awc_read_hpdataset                         | 4-8  |

|   | AEL Trigger Functions                      | 4-8  |

|   | awc_example_trigger                        | 4-8  |

|   | awc_internal_trigger                       | 4-8  |

|   | Comparison AEL Functions                   | 4-9  |

|   | awc_get                                    | 4-9  |

|   | awc_put                                    |      |

|   | awc_settype                                |      |

|   | awc_gettype                                |      |

|   | awc_bconvert                               |      |

|   | awc_find                                   | 4-10 |

| 5 | Mapping Components to HDL                  |      |

|   | Component Mapping, Case 1                  |      |

|   | Component Mapping, Case 2                  | 5-1  |

|   | Arithmetic Operators                       | 5-3  |

|   | Bit Manipulation Operator (Barrel Shifter) |      |

|   | Control Logic Operators                    |      |

|   | General Logic Operators                    |      |

|   | Sequential Logic Operators                 | 5-47 |

|   |                                            |      |

| Digital Communications Components 5-5 | 56 |

|---------------------------------------|----|

| Miscellaneous Operators 5-6           | 63 |

# 6 Mapping Components to Xilinx Cores Index

٧

# **Chapter 1: DSP Synthesis Overview**

DSP Synthesis is an easy-to-use hardware implementation tool that enables you to generate a register-transfer level (RTL) implementation of your design. DSP Synthesis helps you optimize at the macro block-level as opposed to the gate level.

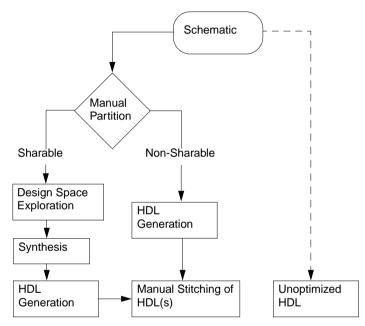

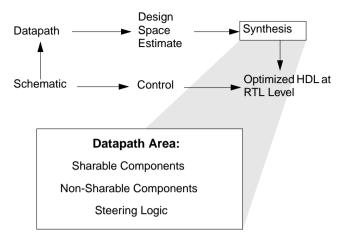

The primary requirement for macro block-level optimization is that the macro blocks be sharable. As a result, a design's algorithmic specification is partitioned into control instructions (serial-parallel conversion, for example), which are non-sharable, and data path instructions (adders and multipliers, for example), which are sharable. Any retiming required of the data path as a result of sharing macro blocks across instructions is done automatically within DSP Synthesis.

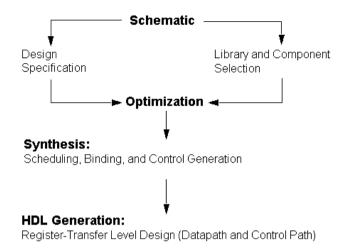

DSP Synthesis uses a schematic made up of synthesizable components to generate HDL (Verilog or VHDL) code. The design may also be optimized at the behavioral level (for factors such as throughput and clock speed) by trading off area with performance. Such trade-offs are typically used to arrive at optimal, cost-effective design solutions for a given problem.

The HDL code can be simulated and the simulation waveform can be compared against the waveform generated from the original schematic simulation.

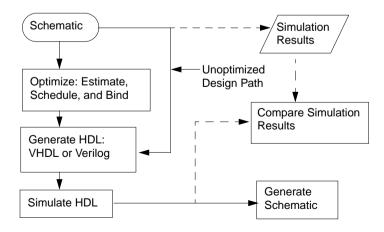

Optimized HDL code can be used for logic synthesis and gate-level optimization in another software application. It can also be used to generate a schematic, if desired. The following is an idealized DSP Synthesis task flow.

DSP synthesis offers you the choice of an un-optimized and an optimized hardware implementation.

- An un-optimized implementation uses a one-to-one mapping of the specification component to a hardware component (VHDL or Verilog). Such an implementation is typically used for control-driven designs with a small number of sharable instructions.

- An optimized implementation requires the partitioning of a design into its control and data path segments. The optimization process uses the data path and library you specify to present you with design options that have varying area and performance values. The refined option is synthesized to generate an optimized control and data path using VHDL or Verilog. The control segment is then added back to complete the overall design.

# Launching DSP Synthesis

DSP Synthesis can be launched either independently or from within Advanced Design System. Depending upon your computer platform and configuration, you can launch DSP Synthesis using any one of the following methods.

To launch DSP Synthesis from a Schematic window:

• Choose Tools > DSP Synthesis > Start DSP Synthesis from the Schematic window menubar for a signal processing design.

When you launch DSP Synthesis in this manner, you will need to open the desired design file for synthesis.

• Choose Tools > DSP Synthesis > Send Design to DSP Synthesis from the Schematic window menubar for a signal processing design.

When you launch DSP Synthesis in this manner, the active design in the Schematic window is automatically loaded for your synthesis tasks.

To launch DSP Synthesis on a UNIX workstation:

• Type **dsynthesis** in a terminal window to launch DSP Synthesis on its own, without launching Advanced Design System.

To launch DSP Synthesis on a PC:

• Double-click the shortcut for DSP Synthesis to launch DSP Synthesis on its own, without launching Advanced Design System.

Click Start > Programs > Advanced Design System 2001 > ADS Tools > DSP Synthesis.

Once the application is launched, the DSP Synthesis window is displayed automatically. This window is used to display the synthesis file you load.

#### **Creating a New Project**

DSP Synthesis uses the Advanced Design System project paradigm. A project acts as an organizer of one or more designs that may be created to accomplish a larger, overall implementation goal. It is used to keep together all the information for designing, analyzing, and synthesizing a design. It is also used to keep together the information generated in creating, simulating, and comparing HDL code.

You will need to create or open a design project before you can begin using DSP Synthesis for your design tasks.

To create a new project:

- 1. Choose File > New Project to display the New Project dialog box.

- 2. Enter a name and path for the new project or click **Browse** and use the New Project File Browser dialog box to define the path.

- 3. Once you have defined a name and path, click **OK** to create the project.

A feedback message is displayed to confirm that the current working directory has been changed to the project you specified. The DSP Synthesis window is then updated and can be used to import any existing synthesis files to the project.

### **Opening an Existing Project**

DSP Synthesis uses the Advanced Design System project paradigm. A project acts as an organizer of one or more designs that may be created to accomplish a larger, overall implementation goal. It is used to keep together all the information for designing, analyzing, and synthesizing a design. It is also used to keep together the information generated in creating, simulating, and comparing HDL code.

You will need to open a design project before you can begin using DSP Synthesis for your design tasks.

To open and work within an existing project:

- 1. Choose File > Open Project and use the Open Project dialog box that is displayed to locate the existing project you wish to use.

- 2. Once you have selected the project you wish to use, click **OK** to open the project and proceed with your digital synthesis tasks.

A feedback message is displayed to confirm that the current working directory has been changed to the project you specified. The DSP Synthesis window is then updated to display the contents of the project.

### Importing a File

Importing a file is the first step toward synthesizing a design. During the import process, DSP Synthesis transforms the behavioral specification in a schematic into an internal format with separate control and data path information. The import process also performs compiler optimizations such as tree-height reduction and variable renaming.

All data generated during the import process is saved in a new file that uses the *.ddb* extension. This file is created in the Synthesis subdirectory within the project directory. The original design file is closed unchanged once the data has been imported.

To import a file from within DSP Synthesis:

- 1. Choose File > Import to import an existing design file. The Import dialog box is displayed to enable you to identify the design file you wish to open and read for import.

- 2. Once you have selected the design file you wish to import, click **Import** to open the file and proceed with the import process.

To import a schematic from a Schematic window within Advanced Design System:

• Choose Tools > DSP Synthesis > Send Design to DSP Synthesis to import the currently displayed design file.

OR

• Choose Tools > DSP Synthesis > Send Selected Components to DSP Synthesis to import only the currently selected components.

DSP Synthesis is launched and the import process is initiated for the design or component.

# **Opening a File**

DSP Synthesis offers the standard file handling and management capabilities. DSP Synthesis uses the.ddb extension for its files. These files are created the first time you import a design into DSP Synthesis, and are typically saved in the Synthesis subdirectory within the project directory.

To open and work with an existing synthesis file:

- 1. Choose File > Open Synthesis File to open an existing synthesis file. The File Open dialog box is displayed to enable you to identify the existing file you wish to open.

- 2. Once you have selected the synthesis file you wish to display, click **OK** to open the file and proceed with your synthesis tasks.

**Note** Only one synthesis file can be open at a time. Be sure you save any changes made to an open file before opening a different file. A synthesis file uses the *.ddb* extension. This file is initially created in the Synthesis subdirectory within the project directory.

#### Saving a File

DSP Synthesis files are created the first time you import a design into DSP Synthesis. These files are typically saved in the Synthesis subdirectory within the project directory.

A synthesis file uses the behavioral specification in a schematic to create an internal format with separate control and data path information. This information, along with any optimization and synthesis data you may have generated during the process of exploring the design space, is stored in the file.

To save changes to a file:

• Choose File > Save to save any changes you have made to the currently open synthesis file.

A DSP Synthesis file transforms the behavioral specification from a schematic into an internal format with separate control and data path information. In addition, it includes compiler optimizations such as tree-height reduction and variable renaming. The data in this file generated during the import process is saved using the *.ddb*

extension. This file is created in the Synthesis subdirectory within the project directory.

# **Copying a File**

A DSP Synthesis file is typically created in the Synthesis subdirectory within the project directory. This file is saved using the *.ddb* extension and it contains the data path and control information from the schematic design. In addition, any optimization and synthesis data you may have generated during the process of exploring the design space is stored in this file.

DSP Synthesis offers the standard file handling and management capabilities for making a copy of a synthesis file. When you make a copy, keep in mind that the copy contains the data found in the synthesis file. Any HDL files that you may have generated are not copied automatically.

To save a copy of the currently open file:

• Choose File > Save As to save a copy of the currently open synthesis file. Use the File Save As dialog box that is displayed to provide a name and location for the file you wish to create.

#### **Closing a File**

DSP Synthesis offers the standard file handling and management capabilities. Even though more than one file or component is used to make up a synthesis file, the interface is designed to present a simple and unified environment.

To close a currently open file:

• Choose File > Close Synthesis File to close an existing synthesis file. The open file is closed and a blank synthesis window is displayed.

# **Using Command Lines**

DSP Synthesis includes features to automate the synthesis process.

To use the command line for automating your synthesis design tasks:

• Choose Options > Command Line to display the Command Line dialog box.

Keeping this dialog box open while you complete your synthesis tasks enables you to automatically generate a list of commands that you can reuse either directly or with any enhancements or parameters you wish to modify.

DSP Synthesis Overview

# **Chapter 2: Behavioral Synthesis Overview**

DSP Synthesis uses a behavioral schematic to create a register-transfer level (RTL) design that consists of a data path specified by hardware components and control elements specified by a state table. Behavioral synthesis enables you to accommodate the growing complexity of designs by exploring large design spaces while reducing design time and errors.

Given a design problem, behavioral synthesis enables you to explore your options across the design spectrum between the two extremes of hardware implementation. Using the throughput requirement and clock cycle, DSP Synthesis provides you design options with varying area-performance trade-offs. That is, it enables you to determine the effects of area reduction on the speed of execution, both latency and throughput, and vice versa.

Using the inputs you provide, estimates for the design options are displayed in a spreadsheet using one row for each design option.

| Design Space<br>E = Fine Estimated; S = Synthesized; (R) = Recommended<br>P = Pipeline Design; NP = Non-Pipeline Design<br>Total number of row(s) selected: 0<br>Estimated (Recommended) Estimated<br>Synthesized (Recommended) Synthesized |                          |              |       |               |              |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|-------|---------------|--------------|---------|

| Status                                                                                                                                                                                                                                      | Master Clock Period (ns) | Design Style | Area  | Thruput (MHz) | Latency (ns) | hp_ADD_ |

| E (R)                                                                                                                                                                                                                                       | 5.2                      | Р            | 12728 | 1.732502      | 577.2        |         |

| E (R)                                                                                                                                                                                                                                       | 5.2                      | Р            | 20040 | 4.930966      | 202.8        |         |

| E (R)                                                                                                                                                                                                                                       | 5.2                      | Р            | 31008 | 9.157509      | 109.2        | -       |

| E (R)                                                                                                                                                                                                                                       | 5.2                      | Р            | 38320 | 12.820513     | 83.2         |         |

| E (R)                                                                                                                                                                                                                                       | 5.2                      | Р            | 49288 | 16.025641     | 67.6         |         |

| E                                                                                                                                                                                                                                           | 5.2                      | Р            | 67428 | 21.367521     | 52           |         |

| E                                                                                                                                                                                                                                           | 5.2                      | Р            | 63912 | 21.367521     | 52           |         |

| E                                                                                                                                                                                                                                           | 5.2                      | Р            | 74880 | 21.367521     | 46.8         |         |

| E                                                                                                                                                                                                                                           | 5.2                      | Р            | 71084 | 21.367521     | 52           |         |

| E                                                                                                                                                                                                                                           | 5.2                      | Р            | 67288 | 21.367521     | 52           |         |

|                                                                                                                                                                                                                                             |                          |              |       |               |              |         |

Figure 2-1. DSP Synthesis Spreadsheet

In a typical DSP system that consists of several hardware components such as a processor, memory, an ASIC, etc., DSP Synthesis can be used to optimize the ASIC design.

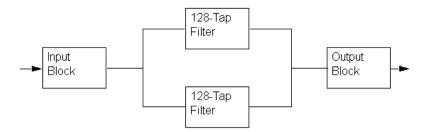

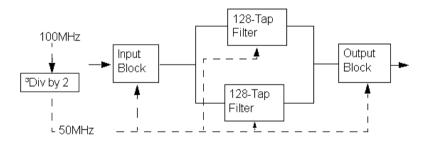

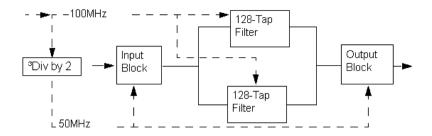

For example, assume that the clock frequency for the following subsystem is 100 MHz, and the throughput requirement of this ASIC is 50 MHz. (The system clock frequency is usually determined by the technology and processes, and not by the ASIC alone.)

In this example, the filter banks are part of the data path block and can be optimized using DSP Synthesis. The input and output blocks do not contain any sharable components, and therefore are separated as a good design practice. For more information on partitioning the design, refer to "Partitioning" on page 2-19.

Given this design, the following two likely design cases illustrate the advantages of using DSP Synthesis to explore the design space before generating HDL.

Case 1: For the simplest hardware implementation of this block, each filter will need one hardware multiplier and one adder per tap for a total of 256 hardware multipliers and 254 hardware adders.

In this case unoptimized HDL code can be generated for the entire design (input, output, and data path blocks) without any design space exploration. For details on generating unoptimized HDL code directly from a schematic, refer to "Generating HDL Code" on page 3-1.

Case 2: In an optimized hardware implementation, the filters will need to produce one result every two clock cycles. This would allow the filters to be implemented using half the hardware adders and multipliers per tap for a total of 128 hardware multipliers and 128 hardware adders.

In this case HDL code for the control blocks (input and output) need to be generated separately. The filter banks can be optimized for a throughput of 50 MHz before the HDL code is generated. The two HDLs can then be manually stitched together to obtain the final HDL code (keep in mind the divide by 2 of the clock). The process of combining HDL code for the control and data path blocks is referred to as *Manual Stitching* in the introductory flowchart describing the DSP Synthesis task.

### **Optimization Overview**

Behavioral synthesis is particularly well-suited for optimizing designs within the application domain of data-dominated DSPs. The following is an idealized task flow of the behavioral synthesis optimization process, which works best for schematics with instructions that can share hardware.

Optimization uses your design and library specifications to generate options with varying area and performance values. The selected optimized option is then synthesized to generate a register-transfer level design that includes the optimized control and data path. Refer to "Estimating Resources" on page 2-28 for details on how resources are estimated. Refer to "Datapath Area" on page 3-12 and "Control and Wiring Area" on page 3-14 for details on how area is estimated for the synthesized data path.

DSP Synthesis also allows you to create designs with fixed throughputs. The main goal is trading off shareable, expensive components (such as multipliers and adders in the example above) with design performance. Resource sharing requires some control overhead and steering logic as well. To control resource sharing, a resource area threshold can be specified. If the area of a sharable resource is smaller than this threshold, the resource is not shared.

### **Using DSP Synthesis**

DSP synthesis offers you a simple and flexible approach to generating an unoptimized or optimized hardware implementation from your design. A generalized DSP Synthesis work flow incorporates one or more of the following steps.

1. Launch DSP Synthesis.

For details on the various methods of launching DSP Synthesis, refer to "Launching DSP Synthesis" on page 1-2.

2. Identify the design.

For details, refer to "Opening a File" on page 1-5 or to "Importing a File" on page 1-4.

3. Define the design specifications.

For details, refer to "Defining the Design Specifications" on page 2-7.

4. Map the library components.

For details, refer to "Selecting a Library" on page 2-22 and "Mapping Components" on page 2-27.

5. Optimize the design.

Skip this step for an unoptimized hardware implementation. For optimization details, refer to "Estimating Resources" on page 2-28.

6. Synthesize the design.

Skip this step for an unoptimized hardware implementation. For optimization details, refer to "Synthesizing Designs" on page 2-32.

7. Generate an output.

For details on the various available options, refer to "Output and Display Overview" on page 3-1.

#### Using the Synthesis Wizard

DSP Synthesis includes a wizard interface that steps you through the process of preparing your design for optimization. This process includes defining the design specifications, selecting the library, and mapping the components.

To use the synthesis wizard for preparing your design, do the following:

1. Launch the synthesis wizard.

Choose **Design** > **Synthesis Wizard** to launch the built-in synthesis specification wizard.

2. Define the design specifications.

For details on defining the design specifications, refer to "Defining the Design Specifications" on page 2-7.

3. Select the library.

For details on selecting a library, refer to "Selecting a Library" on page 2-22.

4. Map the components.

For details on mapping the components, refer to "Mapping Components" on page 2-27.

# **Defining the Design Specifications**

DSP Synthesis uses your design specifications for synthesis. Design specifications can be defined manually or by using the synthesis wizard.

To define the design specifications:

- 1. Display the specification options. Choose **Design** > **New Specification** to display the Specification dialog box where you can select the library, component, and design options. Or choose **Design** > **Synthesis Wizard** to use the synthesis wizard to guide you through the process of selecting the library, component, and design options.

- 2. Select the design specifications.

Use a pipelined style when the input data arrives at regular intervals and high throughput is the design goal. Use a non-pipelined style when the input data arrives at random intervals and a small latency is the design goal. Refer to "Design Styles" on page 2-15 for insights on how design styles affect throughput.

Specify the clock period or the clock frequency (1/clock period). Keep in mind that an optimum clock period is essential for good design and computing efficiency during estimation. Refer to "Clock Periods" on page 2-16 for insights on how clock periods can affect area, throughput, and latency.

### **Design Modes**

There are a number of design modes available in DSP Synthesis. Many of them are described in this section.

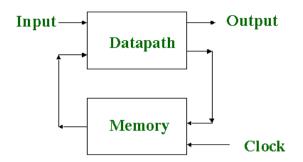

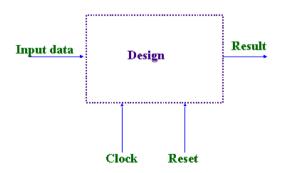

The figure below illustrates a generic structure for a synchronous digital design.

Figure 2-2. Digital Design Review

The DSP Synthesis tool produces a design where the data path performs computation and stores the results in memory. The memory in this figure is divided into two parts: one stores the results of the computation and the other emits control signals to the data path and thus guides the computation performed in a clock cycle.

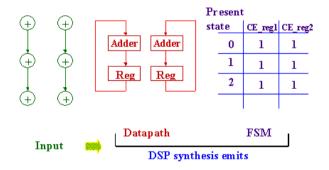

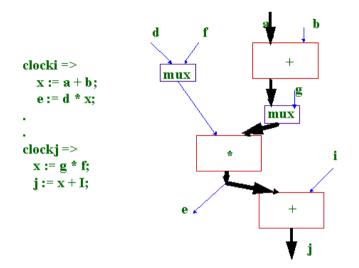

In the figure below illustrates the input-output relationship.

Figure 2-3. Example Design 1

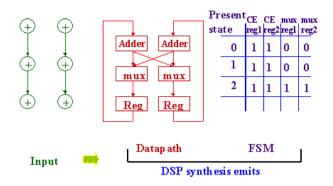

The input to the DSP Synthesis tool is the graph showing the behavior (six additions). The DSP Synthesis tool emits an RTL design that consists of a data path and control that performs the function.

The same input can be realized using different RTL designs (below), some of which are better than others.

Figure 2-4. Example Design 2

The DSP Synthesis tool generates several architectures and presents you the choices. It also ranks the choices by the functional area needed by the design. By this token, the second design is deemed inferior to the first design as it takes more area than the first while delivering the same performance.

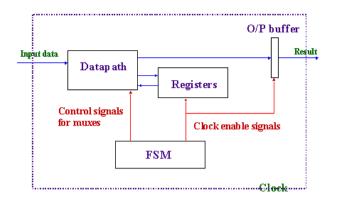

The following two figures illustrate the synthesized design produced by the tool from a users perspective. The internal details of the design are shown in the following figure. Note the buffer at the output.

Figure 2-5. User's View of RTL Design

Figure 2-6. Internal View of RTL Design

### **Timing Parameters**

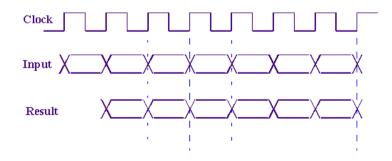

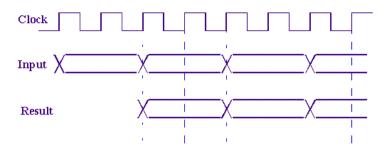

The figure below shows the timing model of a circuit. In this figure, the circuit produces a result one clock after the input is received. This result is stored in the buffer and held steady until the next iteration of circuit execution.

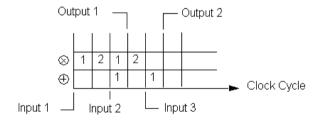

Figure 2-7. Timing Diagram 1

In Timing Diagram 2, the circuit produces one result every two clock cycles. For this design to work correctly, the input value must be held constant for two clocks, and the first result appears at the output after two clocks. Also, the result is held constant for two clocks when it is updated by the new result.

Figure 2-8. Timing Diagram 2

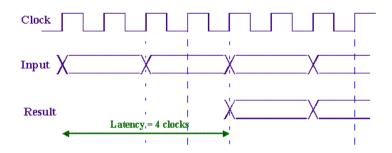

We now define the various timing metrics that are used in DSP Synthesis. Latency is the time needed to compute a result. This is the front-to-end delay of a component or a design. Clock refers to the system clock used to drive the design. It is usually determined by the technology and specified in MHz or its period (ns or ps). Critical path delay is the largest delay between two memory elements. A multi-cycle component (see figure below) is a component whose latency is greater than the clock period. In the above example, if the component latency is 15ns and the clock has a period of 10ns the component requires two clock cycles for execution.

Figure 2-9. Multicycle Component

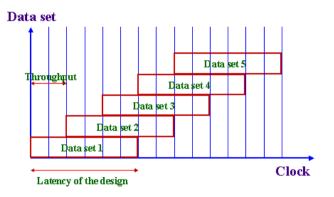

Throughput is defined as the minimum number of clock cycles between two successive data points that can be sent to a component or a design. By the same token, it is also the rate at which the results can be produced. In the figure below, the throughput of the design is one result every two clocks (or, if the clock frequency is 100 MHz, then the throughput is 50 MHz). The latency of the design is four clock cycles. Thus, the first result appears four clock cycles after the input arrives, and after that the design produces one result every two clock cycles.

Figure 2-10. Throughput

Maximum throughput is limited by several factors:

- One result per clock cycle.

- Throughput must be integer-divisible of the clock rate. If the clock frequency is 10 MHz, then a throughput of 7.5 MHz is not possible.

- If there is a multi-cycle component, then the number of cycles of that component limits the throughput. For example, if a multiplier requires two clock cycles for execution, then the throughput cannot exceed one result every two clock cycles.

- If there is a cycle in the input schematic, then throughput cannot exceed: (number of clocks required for the cycle) / (number of registers in the cycle).

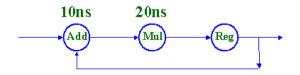

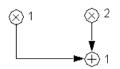

The figure below is used as an example to illustrate maximum throughput limitations.

Figure 2-11. Example for Maximum Throughput

Suppose:

- Add latency = 1 clock

- Mul latency = 2 clocks

Therefore, cycle delay equals 3 clocks. And, maximum throughput is limited to one result every

max(add clock, mul clock, cycle delay/number of registers)

$= \max(1, 2, 3/1) = 3.$

Thus, if the clock frequency is 15 MHz, then throughput cannot exceed 5 MHz.

So, how can we increase the throughput of a design?

- Use faster components

- Use a faster clock

- Chaining

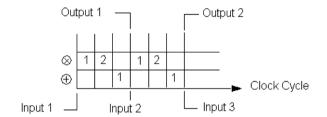

The first two solutions are easy to understand. So let's define chaining. Chaining is the execution of two sequential instructions in one clock, as shown in the next figure.

Figure 2-12. Chaining

Figure 2-13 is the same as the maximum throughput example. If chaining is allowed and a clock with a periodicity of 30ns is used, a throughput of one result every clock cycle can be achieved.

Figure 2-13. Advantage of Chaining

Chaining, however, has its own problems. It may result in false paths in a design. In the figure below, the path shown in darker arrows is never used during the execution of the design. However, since it exists in the design, the timing analyzer may

incorrectly surmise that the critical path in the design has two adders and one multiplier. The false path problem also impacts automatic test-pattern generators (ATPG), since ATPGs could unsuccessfully try to find methods of exciting a false path. The DSP Synthesis tool reports false paths generated by the tool.

Figure 2-14. False Path

.Chaining is useful when the clock period is greater than the component delays, as is shown in the figure below.

| Clock | With Chaining Result<br>Every | Without Chaining<br>Result Every |

|-------|-------------------------------|----------------------------------|

| 30ns  | 30ns                          | 60ns                             |

| 20ns  | 40ns                          | 40ns                             |

| 10ns  | 30ns                          | 30ns                             |

## **Design Styles**

DSP Synthesis can produce two types of designs: non-pipelined and pipelined. A pipelined design example is shown in the following figure.

Figure 2-15. Pipeline Design Style

A non-pipelined design is defined as one whose throughput is equal to the latency. The design style you choose should depend upon two factors: the manner in which the input data is received, randomly or at regular intervals; and the performance goal for your design, higher throughput or smaller latency. Keep in mind that the number of sharable resources also affects the design performance and, therefore, influences the design style used.

Even with the same number of resources, pipelined and non-pipelined styles can lead to different throughputs for the same input. However, given the same number of sharable resources, a pipelined design style typically yields an equal or better throughput.

To illustrate the effect of design style on the throughput, consider non-pipelined and pipelined implementations of the following example that has a clock period of 5 ns and executes two multiplication and one addition operations using one hardware adder and one multiplier. Assume that the hardware has a latency of 5 ns.

In a non-pipelined design a new input can be processed every three clock cycles, leading to a throughput of 1/15 ns = 66.7 MHz.

In a pipelined design a new input can be processed every two clock cycles, leading to a throughput of 1/10 ns = 100 MHz.

As you can see, given identical resources, the throughput of the pipelined design in this example is higher than that of the non-pipelined design. At the same time, the latencies for the design are identical for this example.

#### **Clock Periods**

Clock periods have a significant impact on area and performance. Selecting a clock period that is small in relation to component latency can result in designs with large area, requiring large compute times because each component requires a large number of clock cycles for execution. At the same time, selecting a clock period that is large in relation to component latency can lead to slower designs. For example, a clock period of 0.1 ns in a design with a component latency of 10 ns results in the use of 100 cycles for the execution of each component. And a clock period of 10 ns in a design with a component latency of 4 ns may result in the use of 10 ns for the execution of 4 ns instructions.

In general, a judicious adjustment of the clock period based upon the required number of clock cycles and the latency of the components used is needed to ensure optimum area and performance results.

To illustrate this concept, consider the effect of clock periods on performance in a simple, non-pipelined design with three adders and a multiplier. (Similar reasoning can be applied to the effect of clock periods on area in pipelined designs as well.)

Case 1: If the multiplier latency is 15 ns and the adder latency is 5 ns, a 5 ns clock period is ideal as it yields the following schedule.

In addition to an optimal performance, this schedule illustrates that although the design calls for three add operations, one hardware adder is adequate for an optimal design latency of 5 x 3 = 15 ns.

Case 2: If the multiplier latency is 6 ns and the adder latency is 5 ns, again, a 5 ns clock period is ideal as it yields the following schedule.

In addition to an optimal performance, this schedule illustrates that although the design calls for three add operations, one hardware adder is adequate for an optimal design latency of  $5 x^3 = 15$  ns.

Case 3: If the multiplier latency is 6 ns and the adder latency is 5 ns, a 6 ns clock period yields the following schedule.

This schedule illustrates the effect of a large clock period on design latency which, in this case increases to become  $6 \times 3 = 18$  ns.

Case 4: If the multiplier latency is 4 ns and the adder latency is 5 ns, a 4 ns clock period yields the following schedule.

This schedule illustrates the effect of a small clock period on design latency which, in this case increases to become  $6 \ge 4 = 24$  ns.

Case 5: If the multiplier latency is 4 ns and the adder latency is 5 ns, a 5 ns clock period yields the following schedule.

This schedule illustrates that in some situations a clock period that is larger than the smallest component latency may lead to an optimal design latency,  $5 \ge 3 = 15$  ns in this case.

As the preceding cases illustrate, a judicious adjustment of the clock period based upon the needs and resources of the design is essential for obtaining optimal area-performance results. These cases are not exhaustive and many more scenarios can be constructed. **Note** Registers in DSP Synthesis are assumed to be edge-triggered. A register's clock-enable pin should not be connected.

## Partitioning

Behavioral synthesis optimizes expensive, sharable components in the data path. Components which are not sharable, or not expensive should not be shared. Sending such components to DSP Synthesis only serves to burden the tool with information it cannot effectively use. Thus, partitioning designs prior to synthesis and sending only those parts that can be effectively optimized by DSP Synthesis is a good design practice. For example, if your design consists of a serial-to-parallel converter, followed by a filter, followed by a parallel-to-serial converter, then the only part of this design that can be optimized by DSP Synthesis is the filter. Partitioning the design into three parts and sending only the filter to DSP Synthesis is recommended. Another reason for partitioning designs is for synthesizing multirate designs where different parts of the circuit need to operate at different throughputs. In this case, the design can be partitioned into subsets, each set designed independently and finally the complete design hand-assembled.

A good design practice for generating schematics is to use a modular hierarchy to group the different parts separately. The design process for a partitioned design can then be illustrated as follows:

- 1. Generate partitioned schematic.

- 2. Synthesize and generate HDL of each subset separately.

- 3. Manually stitch the HDLs of each piece. Stitching may need buffers and/or clock dividers. The design model and timing information must be satisfied.

The following examples illustrate the partition and design methodology.

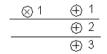

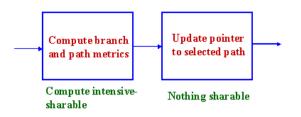

The figure below shows a Viterbi decoder. The decoder consists of two major parts: the computation part and the storage of current best path.

Figure 2-16. Example 1, Viterbi Decoder

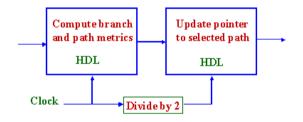

The computation part is best suited for optimization because the storage part has no sharable components and hence is not suitable for DSP Synthesis. Thus, to generate a good design, send the computational part to DSP Synthesis with throughput requirements, say, one result every two clock cycles (i.e., throughput = 1/2 clock frequency) and produce the HDL for this design. Also, produce the HDL (without DSP Synthesis) of the storage part. Notice that the computational part is operating at half the frequency of the storage part. Thus when the two HDLs are stitched, place a clock divider between them, as shown in the following figure.

Figure 2-17. Example 1, Viterbi Decoder, Continued

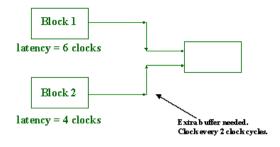

The figure below illustrates the need for a buffer. Suppose the original design is partitioned into three sets and each set is individually synthesized. Suppose blocks 1 and 2 have a latency of 6 and 4 clocks, respectively (the throughput of the two blocks are same in this example and is equal to 1/2 clock frequency). Then in order to ensure that the results of the two blocks arrive at the correct time at the last block, an extra buffer is needed, which must be clocked every two clocks.

Figure 2-18. Example 2

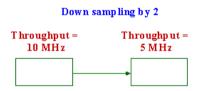

This final example illustrates how to use partitioning for down-sampling by 2. Synthesize both blocks separately, one for 10 MHz throughput and the other for 5 MHz throughput.

Figure 2-19. Example 3

There is no need to use different clocks for driving the two blocks. While stitching the two HDLs together, use an extra buffer in between to hold the input value of the second block. Clock this buffer at 5 MHz while ensuring the phase is correct.

To summarize partitioning:

- 1. Partition.

- 2. Synthesize/generate the HDL, each piece separately.

- 3. Manually stitch the HDLs for each piece.

The stitched code may need a clock divider and/or buffers. Use the design model and timing information to check for these. Make sure the throughput requirements of each block are satisfied and all data arriving at a block are in phase.

# Selecting a Library

DSP Synthesis uses your library choices for determining the components available for mapping during the synthesis process. The options available depend upon the libraries loaded for use.

You can select a library during any one of three processes: while using the synthesis wizard, when specifying the default for future designs, or while generating unoptimized HDL code.

To select the library:

- 1. Display the library options (Options > Library Browser)

- Within the synthesis wizard, define the design specifications and click **Next** to display the library selection options.

- Choose **Design** > **New Specification** to display the Specification dialog box where you can select the default library option for synthesis.

- Choose **Design** > **Generate HDL** to display the HDL Generator dialog box. Click the design file name in the Design Selection field to select the design for which you wish to generate HDL code. Click **Edit Spec** to display the Specification dialog box where you can select the library you wish to use for HDL generation.

- 2. Select a library.

Click a library name from the Mapping Libraries list and click Add to move it to the Selected Libraries list. A brief description of the library is displayed when you select it in the Mapping Libraries list. To remove a library name from the Selected Libraries list, click the library name and click Cut. Refer to "Mapping Libraries" on page 2-22 for details on each library and when it can be used best.

#### **Mapping Libraries**

Each DSP Synthesis library includes the full set of DSP Synthesis models. The HPLib libraries only support HDL generation and include no vendor-specific estimation data; the Xilinx4000e-HPLib and LSI500k-HPLib libraries support synthesis and include vendor-specific estimation data. Keep in mind that selecting components from two or more libraries will result in an overlap. Map to the most appropriate library based upon the HDL language and logic synthesis tools used in the implementation.

| Design Task and Tools                                             | Library                                                                                                |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| HDL generation without targeting Design Compiler                  | "HPLib" on page 2-23                                                                                   |

| HDL generation targeting<br>Design Compiler without<br>DesignWare | "HPLib-Std_Logic_Arith" on page 2-23                                                                   |

| HDL generation targeting<br>Design Compiler using<br>DesignWare   | "HPLib-DesignWare" on page 2-24                                                                        |

| Synthesis without targeting<br>Design Compiler                    | "LSI500k-HPLib" on page 2-24<br>"Xilinx4000e-HPLib" on page 2-26                                       |

| Synthesis targeting Design<br>Compiler without DesignWare         | "LSI500k-HPLib-Std_Logic_Arith" on<br>page 2-25<br>"Xilinx4000e-HPLib-Std_Logic_Arith" on<br>page 2-26 |

| Synthesis targeting Design<br>Compiler using DesignWare           | "LSI500k-HPLib-DesignWare" on page 2-25<br>"Xilinx4000e-HPLib-DesignWare" on<br>page 2-27              |

#### HPLib

- Generic Verilog simulation and synthesis models

- Numeric standard-based VHDL simulation and synthesis models

- Supports HDL simulation

- Verilog synthesis supports both Design Compiler and non-Synopsys logic synthesis tools

- Numeric standard-based VHDL supports non-Synopsys logic synthesis only

Map to if:

Generating HDL code only

### HPLib-Std\_Logic\_Arith

• Generic Verilog simulation and synthesis models with DesignWare based simulation and synthesis models for signed multiplication.

- Standard logic arithmetic based VHDL (Synopsys Design Compiler compatible) simulation and synthesis models

- Verilog and VHDL synthesis supports only Design Compiler logic synthesis

- Utilizes basic DesignWare Library

Map to if:

- Generating HDL code using Verilog or standard logic arithmetic VHDL

- Targeting Design Compiler for synthesis of HDL without vendor-specific estimation data

- Not using DesignWare

#### HPLib-DesignWare

- DesignWare based Verilog simulation and synthesis models. Where a designware equivalent is unavailable, the corresponding generic Verilog equivalent is used

- DesignWare based VHDL simulation and synthesis models. Where a designware equivalent is unavailable, the corresponding generic standard logic arithmetic VHDL equivalent is used.

- Supports only Design Compiler with DesignWare Foundation libraries

Map to if:

- Generating HDL code using Verilog or DesignWare-based VHDL

- Targeting Design Compiler for synthesis of HDL without vendor-specific estimation data

- Using DesignWare

### LSI500k-HPLib

- Simulatable and synthesizable Verilog and numeric standard VHDL

- Memory is NOT synthesizable from the HDL

- Includes estimation data for LSI 500k

- Vendor: LSI

- Process: 500k

Map to if:

- Synthesizing and generating HDL code using Verilog or numeric standard VHDL

- Not targeting Design Compiler for synthesis of HDL with LSI-specific estimation data

### LSI500k-HPLib-Std\_Logic\_Arith

- Simulatable and synthesizable Verilog and standard logic arithmetic VHDL

- Memory is NOT synthesizable from the HDL

- Signed Verilog multipliers use DesignWare-based models

- Includes estimation data for LSI 500k

- Vendor: LSI

- Process: 500k

Map to if:

- Synthesizing and generating HDL code using Verilog or standard logic arithmetic VHDL

- Targeting Design Compiler for synthesis of HDL with LSI-specific estimation data

- Not using DesignWare

### LSI500k-HPLib-DesignWare

- Simulatable and synthesizable DesignWare Verilog and numeric DesignWare VHDL

- Memory is NOT synthesizable from the HDL

- Includes estimation data for LSI 500k

- Vendor: LSI

- Process: 500k

Map to if:

• Synthesizing and generating HDL code using DesignWare Verilog or VHDL

- Targeting Design Compiler for synthesis of HDL with LSI-specific estimation data

- Using DesignWare

#### Xilinx4000e-HPLib

- Simulatable and synthesizable Verilog and numeric standard VHDL

- Memory is NOT synthesizable from the HDL

- Includes estimation data for Xilinx 4000e

- Vendor: Xilinx

- Process: 4000e

Map to if:

- Synthesizing and generating HDL code using Verilog or numeric standard VHDL

- Not targeting Design Compiler for synthesis of HDL with Xilinx-specific estimation data

### Xilinx4000e-HPLib-Std\_Logic\_Arith

- Simulatable and synthesizable Verilog and standard logic arithmetic VHDL

- Memory is NOT synthesizable from the HDL

- Signed Verilog multipliers use DesignWare-based models

- Includes estimation data for Xilinx 4000e

- Vendor: Xilinx

- Process: 4000e

Map to if:

- Synthesizing and generating HDL code using Verilog or standard logic arithmetic VHDL

- Targeting Design Compiler for synthesis of HDL with Xilinx-specific estimation data

- Not using DesignWare

#### Xilinx4000e-HPLib-DesignWare

- Simulatable and synthesizable DesignWare Verilog and VHDL

- Memory is NOT synthesizable from the HDL

- Includes estimation data for Xilinx 4000e

- Vendor: Xilinx

- Process: 4000e

Map to if:

- Synthesizing and generating HDL code using DesignWare Verilog or VHDL

- Targeting Design Compiler for synthesis of HDL with Xilinx-specific estimation data

- Using DesignWare

## **Mapping Components**

Once you have selected the library for a specific design, DSP Synthesis generates the parts list and list of candidates automatically.

Once the list of parts is generated, the list of candidates is displayed. You can view this list sorted by design or candidate. A brief description of the candidate is displayed when you select it in the Library Candidates list. You can also choose to display the non-sharable operations. For details on how components are mapped to their HDL counterparts, refer to "Mapping Components to HDL" on page 5-1.

When mapping components while generating HDL, you also have the option of specifying the number of resources used.

To map the components:

- Choose **Design** > **New Specification** to display the Specification dialog box, select a library and then click the Component Selection tab to map the components automatically.

- Choose **Design** > **Synthesis Wizard** to launch the built-in synthesis specification wizard. Click **Next** to map the components within the synthesis wizard after you have defined the design specifications and the library selection options.

- Choose **Design** > **Generate HDL** to display the HDL Generator dialog box. Click the design file name in the Design Selection field to select the design for which

you wish to generate HDL code. Click **Edit Spec** to display the Specification dialog box. Select a library and then click the Component Selection tab to map the components automatically.

## **Estimating Resources**

Estimation or design space exploration enables you to reduce design time by quickly identifying superior design options.

The estimation process uses the behavioral specifications, clock cycle, and component area and delays to generate estimates of the various design options that range from inexpensive and slow designs to fast and expensive designs. It enables you to make an informed decision on the expected area-performance metrics of a design without going through an exhaustive and computationally expensive process of generating the actual design.

This process uses a two-step approach to estimating resources. Given an input specification and a performance requirement, it estimates the resources needed for execution and, then, the performance of the design given the resources.

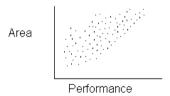

The resources considered for estimation include adders, multipliers, and storage registers. The performance can be measured as either the throughput or the latency of the design. Essentially, estimation involves arriving at an optimal set of points on the area-performance axes. Keep in mind that the estimates are relative, rather than absolute and they may not reflect the final results exactly at this stage.

When you open or import a design into DSP Synthesis and specify your design and library options, an estimate is generated to determine an initial set of possible designs, referred to as the design space. Each row in the spreadsheet represents a design option with its estimated resource requirements and performance.

| Status    | Master Clock Period (ns) | Design Style | Area  | Thruput (MHz) | Later |

|-----------|--------------------------|--------------|-------|---------------|-------|

| (*) E (R) | 6                        | Р            | 12728 | 1.5015        |       |

| (*) E (R) | 6                        | Р            | 20040 | 4.2735        |       |

| (*) E (R) | 6                        | Р            | 31008 | 7.93651       |       |

| (*) E (R) | 6                        | Р            | 38320 | 11.1111       |       |

| (*) E (R) | 6                        | Р            | 49288 | 13.8889       |       |

| (*) E     | 6                        | Р            | 67568 | 18.5185       |       |

| (*) E (R) | 6                        | Р            | 60116 | 18.5185       |       |

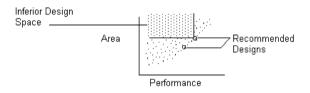

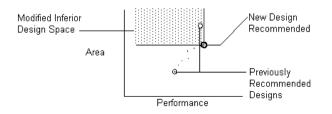

Even within this initial estimate, some design options are identified as recommended. This categorization of designs as recommended is based on the premise that a given design is superior to all of the designs that lie in the quadrant to its upper-left. In other words, it is superior to all other designs that deliver less or equal performance using more area.

For example, an option is considered inferior to another when it delivers the same throughput using more resources or area.

|                    | Status    | r Clock Perio, | Design Style | Area   | hruput (MHz, I |

|--------------------|-----------|----------------|--------------|--------|----------------|

|                    | (*) E (R) | 6              | Р            | 12728  | 1.5015         |

|                    | (*) E (R) | 6              | Р            | 20040  | 4.2735         |

| Decemented         | (*) E (R) | 6              | Р            | 31008  | 7.93651        |

| Recommended Option | (*) E (R) | 6              | Р            | 38320  | 11.1111        |

| Not                | (*) E (R) | 6              | Р            | 49288  | 13.8889        |

| Recommended        | (*) E     | 6              | Р            | 67568  | 18.5185        |

| Option             | (*) E (R) | 6              | Р            | 60116  | 18.5185        |

|                    | (*) E     | 6              | Р            | 136892 | 27.7778        |

|                    | (*) E     | 6              | Р            | 125924 | 27.7778        |

In some situations an option that uses more resources may actually yield better results after synthesis because the extra resources reduce the multiplexing and

wiring costs. For an example that illustrates this, refer to Sharable and Non-Sharable Resources.

Once you arrive at some initial estimates, pick the design options that are closest to your specifications and proceed with fine estimating the design. For details on the fine estimation process, refer to Fine Estimating Resources.

### **Fine Estimating Resources**

Fine estimating resources is an iterative process of exploring design options using this initial data. Select the design options that lie within an acceptable range of area or performance specifications and perform a fine estimation to further explore your options.

• To perform a fine estimation, select the design options and choose **Design** > **Fine Estimation** from the DSP Synthesis menubar.

| (*) E (R) | 6 | Р | 31008  | 7.93651 | 126 |

|-----------|---|---|--------|---------|-----|

| (*) E (R) | 6 | Р | 38320  | 11.1111 | 96  |

| (*) E (R) | 6 | Р | 49288  | 13.8889 | 78  |

| (*) E     | 6 | Р | 67568  | 18.5185 | 60  |

| (*) E (R) | 6 | Р | 60116  | 18.5185 | 60  |

| (*) E     | 6 | Р | 136892 | 27.7778 | 42  |

| (*) E     | 6 | Р | 125924 | 27.7778 | 42  |

Fine estimation takes the design options you identify and explores the design region in greater detail. The attempt in this process is to discover other design options within the range that better meet the design and performance goals. Often this process leads to the identification of options that are superior to those previously selected.

Fine estimation involves repeating this process until no new design options are discovered within the range of your interest.

Once you reach this point, pick the design option that best meets your specifications and proceed with synthesizing the design. For details on the synthesis process, refer to Synthesizing Designs.

### Sharable and Non-Sharable Resources

Synthesizing a design may lead to an increase in the area estimates of a design option. Typically this increase results from the addition of non-sharable resources such as wires, multiplexers, and finite state machines. Consequently, a design option that seemed optimal after fine estimation may become unacceptable after synthesis.

In some situations a design option that uses more resources may actually yield better results after synthesis if the extra resources reduce the multiplexing and wiring costs. As a result, identifying an optimal design option for synthesis involves taking into consideration a trade-off between the use of sharable and non-sharable areas.

To illustrate this concept, consider the following example that estimates and synthesizes the following schematic.

The following three design options are generated as part of the estimation process. The first design option uses the lowest resources and occupies the smallest area. Based upon the area and resource estimates, this option may seem optimal if throughput and latency values are assumed to be within acceptable limits.

| Status    | er Clock Period, | Design Style | Area | Thruput (MHz) | Latency (ns) | TRUNC_S |

|-----------|------------------|--------------|------|---------------|--------------|---------|

| (*) E (R) | 5.2              | Р            | 140  | 64.1026       | 15.6         |         |

| (*) E (R) | 5.2              | Р            | 280  | 96.1538       | 10.4         |         |

| (*) E (R) | 5.2              | Р            | 420  | 192.308       | 10.4         |         |

However, upon synthesis, the area requirements increase dramatically to take into consideration the multiplexing and wiring needs. Synthesizing the second design makes it the recommended option because it uses marginally greater area but yields better throughput and latency.

When all three options are synthesized, the third design becomes the recommended option because it uses the smallest area for significantly superior throughput.

| Status    | er Clock Period, | Design Style | Area | Thruput (MHz) | Latency (ns) | TRUNC_S |

|-----------|------------------|--------------|------|---------------|--------------|---------|

| S         | 5.2              | Р            | 1200 | 64.1026       | 15.6         |         |

| S         | 5.2              | Р            | 1270 | 96.1538       | 10.4         |         |

| (*) S (R) | 5.2              | Р            | 1176 | 192.308       | 10.4         |         |

This simple example illustrates the point that arriving at an optimal synthesized design option requires trade-offs between sharable areas (adders, multipliers, etc.) and non-sharable areas (wires, multiplexors, finite state machines, etc.).

## Synthesizing Designs

Synthesis begins with scheduling a specification from the behavioral or architectural level to the implementation level. Within DSP Synthesis this process uses the number of available components as a guide for assigning the execution of instructions in the behavioral specification to a specific clock cycle.

Scheduling is arguably the most important task in high-level synthesis because a majority of the area-performance trade-offs are made during this process. That is, given the specification and resource allocation, this process attempts to minimize the latency by determining when an instruction will start execution. Depending upon the design style you've specified, pipelined or non-pipelined, scheduling either maximizes the throughput or minimizes the latency of the design.

• To synthesize a design, select the design option and choose **Design** > **Synthesis** from the DSP Synthesis menubar.

Keep in mind that, in many instances, synthesizing a design that uses some extra resources may lead to a more economical solution by reducing the multiplexer, wiring, and other overhead costs. Refer to "Datapath Area" on page 3-12 and Control and Wiring Area for insights on how area estimations are generated within DSP Synthesis.

After scheduling, DSP Synthesis automatically initiates the Binding and Control generation process. This process essentially involves determining which instruction to execute in which component and which value to store in which register. Depending upon the scheduling, binding also adds steering logic between the components. In addition, this process considers overhead such as the multiplexer and wiring costs.

Once the binding is complete, the control is automatically generated and the complete RTL design with its data path and control is generated. For details on generating outputs or displaying the results from a synthesized design, refer to "Output and Display Overview" on page 3-1.

## **Timing Analysis**

Static timing analysis of a synthesized design uses component delays to identify critical paths in the design (wiring delay is not considered). A path starts from a register and ends in a register. A path may span multiple clock cycles (in the case of multi-cycle components) or it may pass through multiple components (in the case of chained components). To perform a timing analysis, follow these steps:

- 1. Open the project (i.e., /examples/tutorial/hdlgen\_prj) in the Advanced Design System Main window.

- 2. Go to the Schematic window and select Tools > DSP Synthesis > Send Design to DSP Synthesis.

- 3. The New Synthesis File dialog box appears. Enter the synthesis file name and click **OK**.

- 4. In the DSP Synthesis window select Design > New Specification.

- 5. The Specification dialog box appears. Highlight the desired mapping library and click Add.

- 6. Click the Component Selection tab followed by OK.

- 7. Click the Design Specification tab. Select a design style, enter the master clock parameters and click **OK**.

- 8. In the DSP Synthesis window, select one of the generated blue designs.

- 9. Select **Design** > **Fine Estimation**.

- 10. Choose another generated blue design.

- 11. Select **Design** > **Synthesis**.

- 12. Choose one of the recommended/synthesized red or pink designs.

- 13. Select **Design** > Timing Analysis.

- 14. The Timing Analysis Result window appears. Click Save.

- 15. In the Save Timing Analysis Result dialog box, enter a file name for the results to be saved in and click **OK**.

# **Chapter 3: Output and Display Overview**

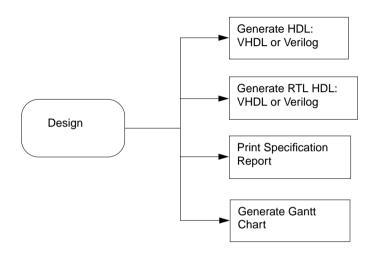

DSP Synthesis offers a variety of output and display options. You can print both a specification report and the results of the design space options generated for the design. Once a design has been synthesized, you can also display a gantt chart of its schedule.

The following is a depiction of the output and display options available within DSP Synthesis.

### **Generating HDL Code**

DSP Synthesis enables you to generate HDL (VHDL or Verilog) code once you have created and simulated a design. To generate HDL, load the design and select the component library. Once you select a library, the design's components are mapped automatically to components available in the library. After the components are mapped, you can generate the HDL code.

To generate HDL code:

1. Load the design.

Choose **Design** > **Generate HDL** to display the HDL Generator dialog box. Click the design name in the Design Selection field to select the design for which you wish to generate HDL code.

You can also choose **Tools** > **HDL Generator** > **Send Design to HDL Generator** from a Schematic window menubar to load the active design.

2. Define the HDL Specifications.

Click **Edit Spec** to display the Specification dialog box where you can select the library and component. For details, refer to "Defining HDL Specifications" on page 3-2.

3. Select the language options.

Define the language and test bench options for generating the HDL code. For details, refer to "Selecting HDL Options" on page 3-3.

4. Define the output file.

Enter the file name and path for storing the HDL code.

5. Generate HDL code.

Click Generate to generate HDL code.

## **Defining HDL Specifications**

Define the specifications you wish to use before generating HDL code. This task can be accomplished on its own or as the second step in generating HDL code, after you have loaded a design.

To define the HDL specifications:

1. Display the specification options.

Choose **Design** > **New Specification** to display the Specification dialog box where you can select the library, component, and design specifications. Alternatively, click **Edit Spec** in the HDL Generation dialog box to display the Specification dialog box. Keep in mind that the design specifications are not available when you display the specifications during the process of generating HDL.

2. Select the library.

Click a library name from the Mapping Libraries list and click Add to move it to the Selected Libraries list. A brief description of the library is displayed when you select it in the Mapping Libraries list. To remove a library name from the Selected Libraries list, click the library name and click **Cut**. For descriptions of the contents of each library, refer to "Mapping Components to HDL" on page 5-1.

3. Select the components.

Click the Component Selection tab to generate the list of parts automatically. Once the list of parts is generated, the list of candidates is displayed. You can view this list sorted by design or candidate. A brief description of the candidate is displayed when you select it in the Library Candidates list. You can also choose to display the non-sharable operations and either view or specify manually the number of resources to be used. For details on how components are mapped to their HDL counterparts, refer to "Mapping Components to HDL" on page 5-1.

4. Select the design specifications.

Click the Design Specification tab to select the design specifications. You can specify a pipelined or non-pipelined style and you can specify the clock period you wish to use. These options are not available when you display the specifications during the process of generating HDL.

If you have been defining the HDL specifications during the process of generating HDL, you may now continue on to the process of "Selecting HDL Options" on page 3-3.

## **Selecting HDL Options**

Define the language and test bench options you wish to use for generating HDL code. This task is typically accomplished during the process of generating HDL code after Defining HDL Specifications.

To define the HDL options:

1. Select the language.

Pick the option you wish to use: Verilog or VHDL.

2. Select the test bench options.

Select the PLI option if you plan to generate Verilog code and wish to use PLI for the file reading functions.

- 3. Select insert input I/O buffer.

- 4. Define the time indexes.

Include test vectors and specify the start and stop time indexes if you plan to simulate the HDL code once it is generated.

5. Define the input dataset.

Enter the name and path for the dataset you wish to use. Alternatively, click **Browse** to browse through the directory structure and specify the name and location of the dataset file.

Once you have selected the HDL options, you may continue with the process of "Generating HDL Code" on page 3-1.

### **Preparing for Verilog Simulation**

Use the following steps to prepare the generated Verilog code for simulation. This process can be accomplished once you have generated Verilog code. For details on generating Verilog code, refer to Generating HDL Code.

To prepare for Verilog simulation:

1. Compile the Verilog code.

Run the help script *<project directory>/synthesis/verilog/compile\_verilog* to retrieve and compile the Agilent EEsof Verilog library files for simulating the generated Verilog code. If you use ModelSim from Mentor<sup>TM</sup>, you can run it to compile both the Agilent EEsof library files and the generated Verilog file. For details on the contents of the help script, refer to Compiling Verilog.

To complete this step on your own, copy and compile the *hp\_arith.v* and *hp\_comp.v* files from the Verilog subdirectory within the Advanced Design System directory (*../dsynthesis/lib/verilog*).

2. Compile and link the PLI C file.

If you use PLI for its file reading functions, you will need to compile the *read.c* file and either link it to the Verilog simulator or make it into a shared library or DLL.

The *read.c* file is located in the Verilog subdirectory within the Advanced Design System directory (*../dsynthesis/lib/verilog*) and it contains instructions for linking it to Verilog-XL, VCS, and MTI.

3. Modify the test bench, as desired.

Within Agilent Ptolemy, an unconnected clock pin is assumed to be connected to a global clock. However, HDL simulation needs a clock waveform. DSP Synthesis adds a clock waveform that starts with a negative clock phase followed by a positive phase. Each phase lasts for a period of timestep/2 time.

Modify this clock waveform to meet your needs.

In addition, you may wish to add values in the test bench for any unconnected global pins such as Set and Low.

4. Simulate the Verilog code.

Compile *\*outfile.v* and simulate. The output values are saved to *\*outfile.out*.

## **Preparing for VHDL Simulation**

Use the following steps to prepare the generated VHDL code for simulation. This process can be accomplished once you have generated VHDL code. For details on generating VHDL code, refer to "Generating HDL Code" on page 3-1.

To prepare for VHDL simulation:

1. Compile the VHDL code.

Run the help script *<project directory>/synthesis/vhdl/compile\_vhdl* to retrieve and compile the Agilent EEsof VHDL library files for simulating the generated VHDL code. For details on the contents of the help script, refer to "Compiling VHDL" on page 3-7.

To complete this step on your own, copy and compile the *hp\_arithutils.vhd*, *hp\_utils.vhd*, *hp\_arith.vhd*, and *hp\_comp.vhd* files from the VHDL subdirectory within the Advanced Design System directory (*../dsynthesis/lib/vhdl*).

2. Modify the test bench, as desired.

Within Agilent Ptolemy an unconnected clock pin is assumed to be connected to a global clock. However, HDL simulation needs a clock waveform. DSP Synthesis adds a clock waveform that starts with a negative clock phase followed by a positive phase. Each phase lasts for a period of timestep/2 time.

Modify this clock waveform to meet your needs.

In addition, you may wish to add values in the test bench for any unconnected global pins such as Set and Low.

3. Simulate the VHDL code.

Compile \*.vhd and simulate. Output values are saved to \*.out.

## **Compiling Verilog**

Use the following example scripts to ascertain the steps you need to take to compile the Verilog code. *compile\_verilog* is an example script for the UNIX workstation, while compile\_verilog.bat is an example script for the PC.

Before you begin to compile, retrieve the Verilog model library files *hp\_comp.v* and *hp\_arith.v*, from the Verilog subdirectory within the Advanced Design System directory (*../dsynthesis/lib/verilog*). The actual commands you then use to compile will be specific to your processes and tools. In general, they should follow the steps illustrated by the following example scripts.

### compile\_verilog

```

cp ../dsynthesis/lib/verilog/hp_comp.v .

cp ../dsynthesis/lib/verilog/hp_arith.v .

rm -rf work

vlib work

vlog hp_comp.v

vlog hp_arith.v

vlog ../synthesis/ls8npli.v

```

### compile\_verilog.bat

```

copy ..\dsynthesis\lib\verilog\hp_comp.v .

copy ..\dsynthesis\lib\verilog\hp_arith.v .

deltree \y work

vlib work

vlog hp_comp.v

vlog hp_arith.v

vlog ..\synthesis\ls8tap.v

```

Once you have compiled the Verilog code, you may continue with the process of "Preparing for Verilog Simulation" on page 3-4.

## **Compiling VHDL**

Use the following example scripts to ascertain the steps you need to take to compile the VHDL code. *compile\_vhdl* is an example script for the UNIX workstation, while *compile\_vhdl.bat* is an example script for the PC.

Before you begin to compile, retrieve the VHDL model library files *hp\_arithutils.vhd*, *hp\_utils.vhd*, *hp\_arith.vhd*, and *hp\_comp.vhd* from the VHDL subdirectory within the Advanced Design System directory (*../dsynthesis/lib/vhdl*). The actual commands you then use to compile will be specific to your processes and tools. In general, they should follow the steps illustrated by the following example scripts.

### compile\_vhdl

```

cp ../dsynthesis/lib/vhdl/hp_arithutils.vhd .

cp ../dsynthesis/lib/vhdl/hp_utils.vhd .

cp ../dsynthesis/lib/vhdl/hp_comp.vhd .

cp ../dsynthesis/lib/vhdl/hp_arith.vhd .

rm -rf work

vlib work

vcom hp_arithutils.vhd

vcom hp_utils.vhd

vcom hp_comp.vhd

vcom hp_arith.vhd

vcom hp_arith.vhd

```

### compile\_vhdl.bat

```

copy ..\dsynthesis\lib\vhdl\hp_arithutils.vhd .

copy ..\dsynthesis\lib\vhdl\hp_outils.vhd .

copy ..\dsynthesis\lib\vhdl\hp_comp.vhd .

copy ..\dsynthesis\lib\vhdl\hp_arith.vhd .

deltree \y work

vlib work

vcom hp_arithutils.vhd

vcom hp_utils.vhd

vcom hp_comp.vhd

vcom hp_arith.vhd

vcom hp_arith.vhd

vcom hp_arith.vhd

```

Once you have compiled the VHDL code, you may continue with the process of "Preparing for VHDL Simulation" on page 3-5.

## Generating RTL HDL

DSP Synthesis enables you to generate register-transfer level (RTL) HDL (VHDL or Verilog) code once you have optimized and synthesized a design. To generate the RTL-HDL, load the design and synthesize one or more design options. Once you have synthesized a design, you can generate RTL-HDL code for it.

To generate RTL-HDL code:

1. Select the design.